Received January 28, 2020, accepted February 27, 2020, date of publication March 10, 2020, date of current version March 19, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2979883

# **CMOS Backplane Pixel Circuit With Leakage and Voltage Drop Compensation for an Micro-LED Display Achieving 5000 PPI or Higher**

JEWOO SEONG<sup>1</sup>, JINWOONG JANG<sup>2</sup>, JAEHOON LEE<sup>2</sup>, AND MYUNGHEE LEE<sup>101,2</sup>, (Member, IEEE)

School of Electrical and Electronic Engineering, Ulsan National Institute of Science and Technology (UNIST), Ulsan 44919, South Korea

<sup>2</sup>Sapien Semiconductors Inc., Seoul 05854, South Korea

Corresponding author: Myunghee Lee (myunghee.lee@unist.ac.kr)

This work was supported by the Korea Institute for Advancement of Technology (KIAT) through the Korea Government (MOTIE) (Competency Development Program for Industry Specialist) under Grant N0001883.

**ABSTRACT** Micro-displays based on micro-LEDs are becoming more and more attractive in AR/MR (Augmented/Mixed Reality) applications. A display size of 0.5 to 0.7-inch is preferred, with 5,000 PPI (Pixel Per Inch) or higher. Due to this pixel density and size, a CMOS (Complementary Metal-Oxide-Silicon) backplane is an ideal solution to drive these pixelized micro-LEDs. As the required pixel size gets smaller, the design of the appropriate pixel circuit becomes more challenging. The simplest 2T1C (2 transistors & 1 capacitor) pixel circuit has potential problems, due to the leakage current of the switch transistor and the voltage drop on the matrix array layout. In this paper, a pixel circuit is proposed as a solution to overcome these two issues. Our simulation results show that the variation of the driving current to the LED is improved by 95 %, and the IR drop error rate is around 2.2 % compared to the 2T1C circuit. The test results also show that the error rate of I<sub>PIXEL</sub> for the whole region of display is under 2.5 %. This work is verified using a test chip implementation with 180 nm CMOS process technology.

**INDEX TERMS** Micro-LED display, microdisplay, high-resolution, DRAM type, voltage driving, low leakage switch, IR drop compensation, CMOS backplane, and high-PPI.

## I. INTRODUCTION

Micro-display technology based on micro-LEDs is still in the early stages of commercial deployment, but it is expected to slowly replace the existing display technologies, such as LCDoS (Liquid Crystal Display on Silicon) or OLEDoS (Organic Light Emitting Diode on Silicon) displays, for certain applications [1]. One of the biggest hurdles for commercializing micro-LED displays is the transfer technology by which the pixelized LEDs are attached to the backplane. Because of this, the following applications are likely to be among the early adopters of these micro-LED displays. The first are micro-display applications for AR/MR (Augmented-/Mixed-Reality), where the silicon CMOS backplane IC and LEDs are hybridized by wafer-to-wafer bonding [2]. The second are super-size display applications, such as outdoor signage or TV screens larger than 110 inch,

The associate editor coordinating the review of this manuscript and approving it for publication was Mahmoud Al Ahmad.

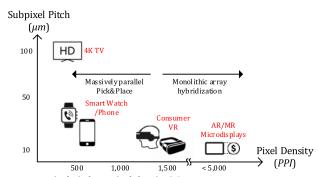

FIGURE 1. Pixel pitch vs. pixel density [1].

which cannot be manufactured using the existing glass-based flat panel displays [3]. Fig. 1 shows the requirements for each display application in terms of pixel pitch and their pixel density, or PPI.

AR/MR applications require a pixel density of 5,000 PPI or higher for 0.5- to 0.7-inch displays. Thus, recent research has concentrated on these requirements [4], [5].

As shown in Fig. 1, the pixel pitch for AR/MR should be in the range of 2  $\mu$ m  $\sim$  5  $\mu$ m. The display size of the microdisplay is less than 1 inch [6], [7]. For this reason, silicon CMOS process technology is an ideal solution that lets us manufacture a backplane with a smaller pixel size [8] and integrated peripheral circuitry.

Each pixel contains a current-driving circuit in order to drive the micro-LED. The maximum driving current to each LED is in the range of a couple of micro-ampere due to the size of the LED. The brightness of the LED is directly proportional to the driving current. The pixel size required by a certain application confines the freedom of the pixel circuit design.

In general, there are two approaches to driving the LED in such high PPI display applications. The first one, PAM (Pulse Amplitude Modulation), is the analog control of pixel current or voltage in order to adjust gray level. The other is PWM (Pulse Width Modulation), in which the gray level is adjusted by controlling the turn-on time of the LED using a maximum driving current. The PAM scheme is often called "voltage driving", since the voltage information is used to control the driving current level to the LED. On the other hand, PWM is often called "current driving" or "digital driving", since it uses a fixed driving current while controlling the pulse width to adjust the light intensity of the LED.

The PAM driving scheme can easily achieve a higher pixel density, per a given display size, thanks to a relatively simple pixel circuit structure. However, the leakage current at the transistors of the pixel circuit deteriorates the display uniformity. It also requires rather complex peripheral circuitry, which results in higher power consumption. The PWM driving scheme needs higher transistor counts in the pixel circuit compared to the PAM scheme, since it requires combinational logic gates and SRAM (Static Random-Access Memory) cells. However, it has the advantage of using a simpler peripheral circuitry with less power consumption.

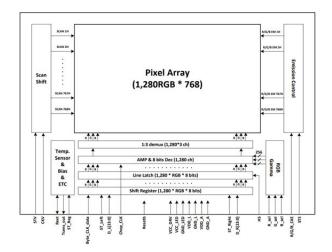

This paper proposes a CMOS backplane based on a PAM-based pixel circuit, along with a solution to the leakage current and IR drop problems. A display resolution of 1280RGB x 768 is used to verify the proposed backplane. The driving current to each micro-LED is limited to a maximum of 2  $\mu$ A after consideration of the total power consumption of the display module.

# **II. 2T1C PIXEL CIRCIUT**

## A. 2T1C CIRCUIT

A CMOS backplane contains two main function blocks: an active-matrix pixel array, and its peripheral circuit to drive the pixel array. All these functions are included on a single silicon backplane [9]. The pixel circuit stores the display data in a voltage form and converts it into a current form to drive the LED, while maintaining its value during a given frame time ( $T_{FRAME}$ ).

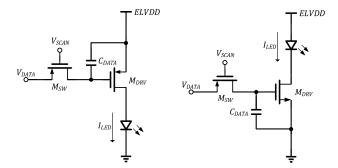

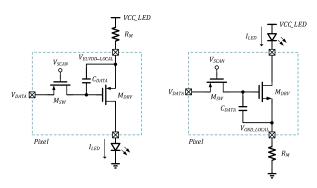

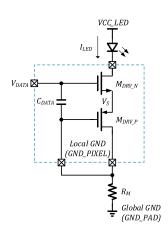

The simplest pixel circuit is a 2T1C structure, as shown in Fig. 2 [10], [11]. Micro-LEDs can be configured by either

FIGURE 2. 2T1C pixel circuit: common cathode (left) & common anode (right).

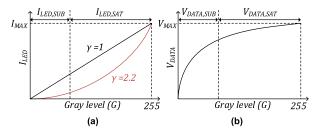

FIGURE 3. The LED grayscale curve of a pixel: Current vs Grayscale (a), Voltage vs. Grayscale (b).

common-cathode or common-anode topology. The pixel circuit consists of only three components: a switch transistor  $(M_{SW})$ , a driving transistor  $(M_{DRV})$ , and a storage capacitor  $(C_{DATA})$ . The basic operation is as follows: when  $M_{SW}$  is turned on by  $V_{SCAN}$ , the value of  $V_{DATA}$  is stored at  $C_{DATA}$ , which sets the  $V_{GS}$  bias of  $M_{DRV}$ . Then, the voltage level stored at  $C_{DATA}$  is converted by  $M_{DRV}$  to the amount of current going to an LED ( $I_{LED}$ ), which consequently controls the light intensity. Even after  $M_{SW}$  is off, its current level is kept by the charge stored at  $C_{DATA}$ . Therefore, maintaining the charge during a given frame time is critical to ensuring the consistent light intensity of the LEDs.

A typical display for an AR/MR application requires grayscale with at least 8-bit or 256 gray levels of a color. The driving current,  $I_{LED}$ , is proportional to the light intensity of an LED. It often has a non-linear relationship to the gray scale input, as shown in Fig. 3(a). A typical display uses a specific value of the gamma correction value,  $\gamma = 2.2$ .  $I_{LED}$ is determined by [12]

$$I_{LED} = I_{MAX} \left(\frac{G}{255}\right)^{\gamma} = \alpha \cdot G^{\gamma} \tag{1}$$

where  $\alpha$  is  $I_{MAX}/255^{\gamma}$ , and G is the grayscale input with 256 gray levels. ILED has different values depending on the subthreshold and saturation region of  $M_{DRV}$ , as shown below: [13]

$$I_{LED,SUB} = \eta e^{\frac{(V_{GS} - V_{TH})}{S}} \tag{2}$$

$$I_{LED,SUB} = \eta e^{\frac{(V_{GS} - V_{TH})}{S}}$$

$$I_{LED,SAT} = k \left(\frac{W}{L}\right) (V_{GS} - V_{TH})^2$$

(3)

where  $\eta$  is a scale factor [14], S is the subthreshold swing of the transistor, k is the process transconductance parameter, and  $V_{TH}$  is the threshold voltage of  $M_{DRV}$ . Assuming that the switch transistor is ideal, (1), (2), and (3) produce the relationship between  $V_{DATA}$  and G as

$$V_{DATA.SUB} = S\gamma \ln G + C \tag{4}$$

$$V_{DATA,SAT} = \alpha' G^{\frac{\gamma}{2}} + V_{TH} \tag{5}$$

where  $\alpha'$  is  $\alpha/\sqrt{k(W/L)}$ , and C is  $V_{TH}+S \ln (\alpha/2\eta)$ . With a typical gamma correction value of  $\gamma=2.2$ , the  $V_{DATA,SUB}$  has a logarithmic relationship to G, and the  $V_{DATA,SAT}$  is proportional to  $G^{1.1}$ , as shown in (4), (5) and Fig. 3(b).

Assuming the maximum voltage of the  $V_{DATA}$  is 1.8 V, the step size of  $V_{DATA}$  for the gray scale at the lower gray region is around 162 mV. However, in the higher grayscale region it would be as small as 1.4 mV. This means that the grayscale of the LED light will be affected by just a few mili-volt difference in the  $V_{GS}$  value of  $M_{DRV}$ . On the other hand, the step size of  $I_{LED}$  has the opposite tendency, since it is quadratically proportional to the  $V_{GS}$  of  $M_{DRV}$ . Thus, it has a smaller value in a low grayscale region, and a larger value in a high grayscale region. Table 1 shows the minimum step size of those parameters in each grayscale region. The mismatch problem becomes critical, regardless of whether grayscale is in the low or high region.

TABLE 1. Gamma Step size of  $V_{DATA}$  and  $I_{LED}$  assuming maximum  $V_{DATA} = 1.8 \text{ V}.$

| Grayscale<br>region | $\Delta V_{DATA}$ | $\Delta I_{LED}$ | Critical<br>parameter |

|---------------------|-------------------|------------------|-----------------------|

| Lowest (0-1)        | 162 mV            | 34.7 pA          | $\Delta I_{LED}$      |

| Highest (254-255)   | 1.4 mV            | 16.4 nA          | $\Delta V_{DATA}$     |

The mismatch among pixel circuits of the array would severely affect the uniformity of the display. Thus, it is necessary to minimize the mismatch between the  $V_{DATA}$  among the pixel circuits.

# B. THE PROBLEM OF THE 2T1C CIRCUIT

There are many variations on the basic 2T1C circuit to improve the performance of the pixel circuit [15], [16]. The  $V_{GS}$  bias of  $M_{DRV}$  in the 2T1C circuit should be maintained during a given frame time ( $T_{FRAME}$ ) to display the target gray scale. Therefore, the amount of charge at  $C_{DATA}$  should not be changed during a given frame time. However, leakage current affects the amount of charge at the storage capacitor. This becomes worse when there is limited space for the storage capacitor due to the allowable pixel size. Therefore, a compensation technique for the leakage current must be considered.

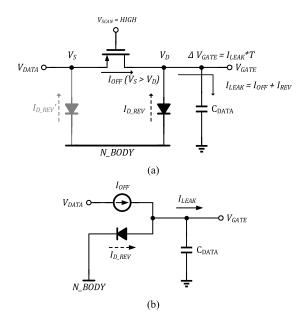

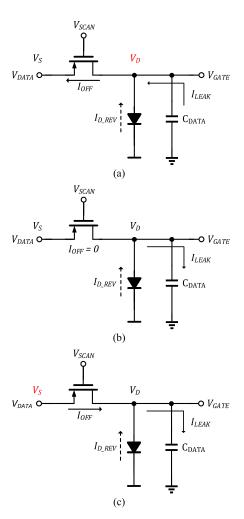

Fig. 4 shows a model of a switch transistor, including its leakage current. The leakage current,  $I_{LEAK}$ , can be expressed as

$$I_{LEAK} = I_{OFF} + I_{D-REV} \tag{6}$$

FIGURE 4. (a)  $I_{LEAK}$  model on switch device and  $C_{DATA}$ , (b) simplified circuit.

where  $I_{OFF}$  represents the off-current through the channel under the gate of the switch transistor, and  $I_{D\_REV}$  is the reverse-bias current of the parasitic diode of the switch transistor.

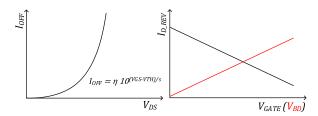

$I_{LEAK}$  is represented as a summation of  $I_{OFF}$  and  $I_{D\_REV}$ , which can be expressed as below [13]:

$$I_{OFF} = \eta e^{-\frac{V_{TH}}{S}} \tag{7}$$

$$I_{D\_REV} \propto V_{D\_REV}$$

(8)

where  $V_{D\_REV}$  is the applied reverse bias [17]. Equation (7) shows  $I_{OFF}$  at  $V_{GS}=0$  [14], which is a function of  $V_{TH}$ . Fig. 5 shows the leakage current behavior based on the bias parameter.

FIGURE 5. Current depending on bias condition:  $I_{OFF}$  (left) &  $I_{REV}$  (right).

According to (7) and (8),  $I_{OFF}$  increases as the  $V_{TH}$  of the switch transistor decreases, while  $I_{D\_REV}$  decreases as the  $V_{BD}$ , the body-drain voltage, decreases.  $I_{D\_REV}$  cannot be controlled by design because  $V_{GATE}$ , the drain of the switch transistor, is always set by the image data value. Therefore, only  $I_{OFF}$  can be controlled by the design parameters. It can be found using the following:

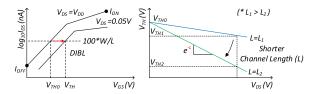

$$V_{TH} = V_{TH0} - (V_{DS}) e^{-L/l_d}$$

(9)

where  $V_{TH0}$  is the intrinsic threshold voltage of a transistor,  $V_{DS}$  is the applied drain-source bias, L is the drawn gate length, and  $l_d$  is the minimum gate length. It is shown in Fig. 6.

FIGURE 6. I<sub>OFF</sub> characteristic (left) & V<sub>TH</sub> role-off (right).

Equation (9) shows that the  $V_{TH}$  of the transistor is dependent on  $V_{DS}$ . This phenomenon is called the DIBL (Drain-Induced-Barrier-Lowering) effect [18]. When the finer CMOS process technology is used,  $I_{OFF}$  increases due to the short-channel effect. This means that the smaller the  $V_{DS}$ , the smaller the  $I_{OFF}$ .

Depending on the bias condition at the source and the drain node of the switch transistor,  $I_{LEAK}$  can flow in either direction and then affect the amount of charge at  $C_{DATA}$ . This change in the charge amount directly affects not only the  $V_{GS}$  bias of the driver transistor, but also the gray scale.

Fig. 7 and Table 2 show three cases of the bias condition at the switch transistor. Assuming that  $I_{D\_REV}$  always flows in the direction of the charging  $C_{DATA}$  due to the reverse-biased diode,  $I_{LEAK}$  can be categorized into three cases: 1) when  $V_D > V_S$ ,  $I_{OFF}$  flows in the direction of the discharging  $C_{DATA}$ ; 2) when  $V_D \approx V_S$ ,  $I_{OFF}$  is almost zero and  $I_{LEAK}$  is determined only by  $I_{D\_REV}$ , (in this case,  $C_{DATA}$  is charging); 3) when  $V_S > V_D$ ,  $I_{OFF}$  flows in the direction of the charging  $C_{DATA}$ . This should be considered the worst case.

TABLE 2. ILEAK cases with bias condition.

| Case        | I <sub>OFF</sub> | I <sub>LEAK</sub>              | C <sub>DATA</sub><br>(or V <sub>GS</sub> ) | Worst<br>Pattern | Re-<br>marks |

|-------------|------------------|--------------------------------|--------------------------------------------|------------------|--------------|

| $V_D > V_S$ | $I_{OFF} < 0$    | - $ I_{OFF} +$<br>$I_{D\_REV}$ | Discharged                                 | White →<br>Black | -            |

| $V_D = V_S$ | $I_{OFF}=0$      | $I_{D\_REV}$                   | No change                                  | -                | Best         |

| $V_D < V_S$ | $I_{OFF} > 0$    | $ I_{OFF}  + I_{D\_REV}$       | Charged                                    | Black →<br>White | Worst        |

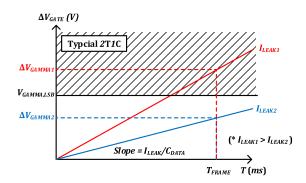

Whatever the case, ideally the change in  $V_{GS}$  or  $|\Delta V_{GS}|$  due to the leakage current would be small enough not to affect the target gray scale during the given frame time. In other words,  $|\Delta V_{GS}|$  should be less than  $|\Delta V_{GAMMA}|$ , as in

$$|\Delta V_{GS}| = \frac{I_{LEAK} \cdot T_{FRAME}}{C_{DATA}} < |\Delta V_{GAMMA}| \qquad (10)$$

where  $T_{FRAME}$  is the frame time of the display, and  $\Delta V_{GAMMA}$  is the voltage step of a gray scale.  $|\Delta V_{GAMMA}|$  varies in each of the lines because of the nature of the array driving pattern. The resolution of the  $V_{DATA}$  step size is different at the

FIGURE 7.  $I_{LEAK}$  tendency on  $C_{DATA}$ : (a)  $V_D > V_S$ , (b)  $V_D = V_S$ , (c)  $V_D < V_S$ .

FIGURE 8.  $\Delta V_{GATE}$  with  $I_{LEAK}$  on the  $C_{DATA}$  graph.

higher- and lower-gray scale regions. Unfortunately, in a typical 2T1C,  $|\Delta V_{GS}|$  is greater than  $|\Delta V_{GAMMA}|$  because of the large leakage current. Fig. 8 shows a linear curve representing the ratio between  $I_{LEAK}$  and  $C_{DATA}$ .  $I_{LEAK}$  should be reduced enough to lower the curve slope, so that the  $\Delta V_{GAMMA}$  during a given  $T_{FRAME}$  is less than the minimum step size of the gamma curve,  $V_{GAMMA,LSB}$  in the case of  $I_{LEAK2}$ .

According to (7), the capacitance should be maximized at a given pixel dimension, while minimizing the leakage current.

FIGURE 9. Pixel Circuit model for an IR drop.

When a smaller pixel dimension is required, there is a tradeoff between the capacitance value and the leakage current.

Another critical problem is the IR drop, caused by the metal routing trace between the reference node for each pixel and the global reference node or I/O pad for the backplane [19]. Due to the layout constraints of the pixel array, the power/reference node for  $V_{DATA}$  and  $V_{GS}$  does not use the same reference point. As explained earlier, the driving current to an LED is determined by the  $V_{GS}$  of  $M_{DRV}$ , which comes from the  $V_{DATA}$ . This means that the  $I_{LED}$  can be different from the expected value, due to the IR drop in the pixel circuit. Therefore, the real display image would have a deviation from the target display image. This problem becomes more severe at a lower gray scale, since the step size of the lower gray scale would be in the range of  $\sim$ pA. Fig. 9 represents a modee metal line,  $R_M$ , connected to the source of  $M_{DRV}$ . Equation (11) shows that  $V_{DATA}$  deviates in the metal line as follows:

$$V_{DATA} = V_{GS} + V_{DROP} \tag{11}$$

where  $V_{DROP}$  can be expressed as

$$V_{DROP}|_{k^{th} \ pixel} = \sum_{1}^{n} (n-k)^2 R_M I_{LED}$$

(12)

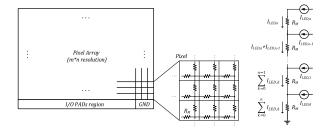

where k represents the row number of the display, n the whole row number of the display, and  $R_M$  the resistance of the metal routing trace. Equation (12) shows that  $V_{DROP}$  with the  $k^{th}$  pixel can vary on a specific pixel location inside the array and the mode of the display. In this case, it is assumed that the  $I_{LED,k}$  in all rows are the same. The I/O pads are placed on the bottom perimeter of the backplane, so the  $V_{DATA}$  of the top pixel has the worst voltage drop. Fig. 10 shows an example of the IR drop on a pixel array. Even if exactly the same image data or  $V_{DATA}$  is written into all pixels, each micro-LED would have a different brightness, which in turn would affect the uniformity of the display image. It could also become worse when the total number of pixels increases.

In summary, the 2T1C pixel circuit has the advantage of achieving smaller pixel dimensions, but the display image is prone to leakage, as well as an IR drop problem. In order to achieve a smaller pixel size with a uniform display, a more sophisticated pixel circuit is required.

**FIGURE 10.** Simple example with IR drop issue for  $R_{GND}$  on a pixel array.

# **III. PIXEL CIRCUIT DESIGN**

# A. LEAKAGE CURRENT

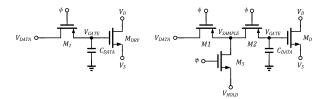

In order to minimize the leakage current, a "T-Switch" structure has been introduced [20]. Fig. 11 shows the structure of the "T-Switch".  $I_{OFF}$  is greatly reduced with this structure, thanks to  $V_{HOLD}$  which modifies (7) so that it becomes

$$I_{OFF} = \eta e^{\left(\frac{-V_{HOLD} - V_{TH}}{S}\right)} \tag{13}$$

where  $V_{HOLD}$  is the bias voltage connected to  $V_{SAMPLE}$  through the switch transistor,  $M_3$ . However, this scheme adds an extra transistor and bias source,  $V_{HOLD}$ , to the pixel circuit. This addition could become a burden in the layout when the pixel size gets smaller.

FIGURE 11. Conventional (left) and improved (right) pass gates structure introduced in [16].

In this paper, we investigated alternative solutions which aim to minimize the leakage current. The first is to use a ground reference instead of  $V_{HOLD}$  at the source node of  $M_3$ , thus removing the extra bias requirement, as shown in Fig. 12. If the switch control signal,  $\phi$ , is low,  $M_3$  is off while  $M_1$  &  $M_2$  are on. In this case,  $V_{GATE}$  becomes the same as  $V_{DATA}$ . When the transistors  $M_1$  &  $M_2$  are off, then  $V_{GATE}$  and  $V_{DATA}$  nodes are disconnected. The intermediate node,  $V_{SAMPLE}$ , is set to the ground reference. This reduces the  $I_{OFF}$  of  $M_2$  at the lower gray levels, thereby avoiding the above-mentioned worst  $I_{LEAK}$  case. However, this approach still has a problem

FIGURE 12. Conventional (left) and improved (right) pass gates with the first proposed method.

at higher gray levels, where  $I_{OFF}$  increases as the  $V_{DS}$  of  $M_2$  becomes the highest value.

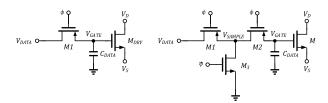

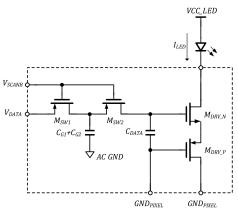

The other approach investigated here is to simply split the switch transistor into two transistors in series, as shown in Fig. 13. This scheme creates a  $V_{SAMPLE}$  node with the parasitic capacitors,  $M_1$  and  $M_2(C_{G1}, \& C_{G2})$ , without requiring an extra bias voltage. It reduces the difference between  $V_{GATE}$  and  $V_{SAMPLE}$  by delaying the change of  $V_{SAMPLE}$  with  $C_{G1}\& C_{G2}$  because the  $V_{SAMPLE}$  usually follows the  $V_{DATA}$ . Therefore, the  $V_{DS}$  of  $M_2$  is close to zero, minimizing the  $I_{OFF}$  of  $M_2$  across the entire gray scale. In addition, it does not require the extra transistor, as is the case in Fig. 12.

FIGURE 13. Conventional (left) and improved (right) pass gates with the second proposed method.

#### B. IR DROP

To alleviate the IR drop problem, the  $V_{GS}$  bias of the  $M_{DRV}$  should be independent of any ground reference. Fig. 14 illustrates the proposed solution by adding a transistor to avoid the problem caused by the IR drop. Unlike the 2T1C pixel circuit, the bias current to the LED is determined by a combination of the gate-source voltages of  $M_{DRV\_N}$  and  $M_{DRV\_P}$ . The  $M_{DRV\_P}$  configured with a PMOS is always on, because the gate is connected to the local reference node, and the current of the pixel is determined to be

$$I_{LED} = k_n \frac{W}{L} (V_{DATA} - V_S - V_{THN})^2$$

$$= k_p \frac{W}{L} (V_S - V_{THP})^2$$

(14)

where  $k_n$  and  $k_p$  are the process transconduction parameters of each MOSFET, and  $V_S$  is the source voltage at each of  $M_{DRV\_N}$  and  $M_{DRV\_P}$ .

FIGURE 14. Pixel Structure with an IR drop compensation.

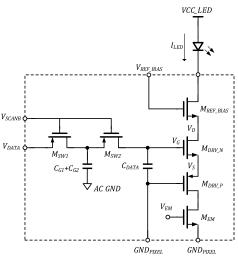

# C. PROPOSED PIXEL CIRCUIT

Fig. 15 shows the proposed pixel circuit, 4T1C, which combines a low leakage switch structure and an IR drop compensation circuit.

FIGURE 15. Proposed sub-pixel circuit with a solution of subthreshold leakage and IR drop.

The pixel size of the 4T1C pixel circuit can be minimized by using a low breakdown voltage transistor with the minimum gate length at any given CMOS process. However, the transistor directly connected to the LED of the pixel should have a high enough breakdown voltage, because the LEDs often use a higher supply voltage than the ones used in normal logic transistor devices, due to the turn-on voltage requirement of the LEDs. In this paper, a 1.8 V power supply is used for the logic transistors. Therefore, a transistor with a high breakdown voltage,  $M_{REF\_BIAS}$ , is added in order to provide a voltage clamp, as shown in Fig. 16. The voltage at the drain of  $M_{DRV\_N}$  can be arbitrarily set by adjusting the  $V_{REF\_BIAS}$  connected to the gate. The  $V_{REF\_BIAS}$  is determined by the following expression:

$$I_{PIXEL} = k_{BIAS} \frac{W_{BIAS}}{L_{BIAS}} \left( V_{REF-BIAS} - V_D - V_{TH} \right)^2 \quad (15)$$

where  $k_{BIAS}$  is the conduction parameter of  $M_{BIAS}$ , and  $V_D$  is the drain voltage of  $M_{BIAS}$ .

FIGURE 16. Completed sub-pixel circuit.

#### IV. SIMULATION AND MEASUREMENT RESULTS

#### A. SIMULATION RESULTS

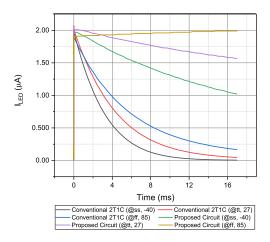

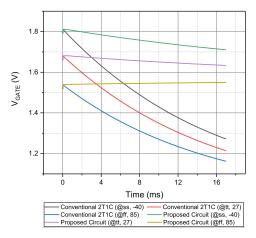

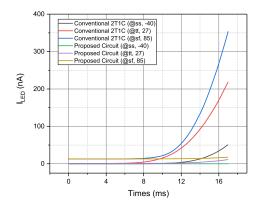

Fig. 17 shows the pixel current ( $I_{LED}$ ) behavior with different switch transistor configurations.  $V_{DATA}$  is set to the condition where the switch leakage current,  $I_{LEAK}$ , reaches the maximum. For the simulation, we used the image pattern of the white image data on the first line of the array and the black image data on the next line (WB...B Pattern). The simulation time was set as one frame time, or 16.6 ms. As shown in Fig. 17 and Table 3,  $I_{LED}$  at 2T1C circuit changed significantly during the one frame time, to 45.2 nA from 2  $\mu$ A at the typical process corner, and to 4.43 nA at the worst process corner. With the proposed pixel circuit, it changed a lot less: to 1.57  $\mu$ A at the typical process corner model, and to 1.02  $\mu$ A at the worst process corner. Thus,  $I_{LED}$  leakage is improved by 75.9 % at the typical corner and 51.3 % at the worst corner.

FIGURE 17.  $I_{LED}$  leakage (White to Black) with conventional 2T1C circuit and proposed pixel circuit.

**TABLE 3.**  $I_{LED}$  behavior at 1 frame time ( $T_{FRAME}$ ).

| Pattern      | 2T1C Pixel        | Proposed Pixel    | Improvement |

|--------------|-------------------|-------------------|-------------|

| WB "B        | 45.2 nA (typical) | 1.57 μA (typical) | 75.9 %      |

|              | 4.43 nA (worst)   | 1.02 μA (worst)   | 51.3 %      |

| $BW\cdots W$ | 219 nA (typical)  | 11.3 nA (typical) | 94.8 %      |

|              | 354 nA (worst)    | 17.7 nA (worst)   | 95.0 %      |

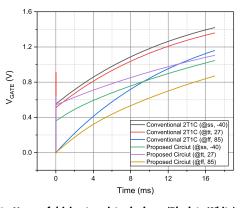

The simulation results of other cases are shown in Fig. 18, Fig. 19, and Fig. 20, Table 3, and Table 4. As shown in these figures and tables,  $I_{LED}$  and  $V_{GATE}$  behavior in the proposed circuit is improved in all cases, compared to the conventional 2T1C circuit.

Fig. 21 shows the error rate of the  $I_{LED}$  in the proposed pixel circuit under an IR drop in the local GND line, which is from the global GND line on the I/O pads. The IR drop error rate is defined using the following equation [19]:

$$Error \ rate(\%) = \frac{I_{LED0} - I_{LED}}{I_{LED0}} \times 100 \tag{16}$$

FIGURE 18.  $V_{GATE}$  of driving transistor leakage (White to Black) with conventional 2T1C pixel circuit and proposed pixel circuit.

FIGURE 19.  $I_{LED}$  leakage (Black to White) with conventional 2T1C pixel circuit and proposed pixel circuit.

FIGURE 20.  $V_{GATE}$  of driving transistor leakage (Black to White) with conventional 2T1C pixel circuit and proposed pixel circuit.

where  $I_{LED0}$  is the driving current in the ideal case, and  $I_{LED}$  is the driving current with an IR drop. In the case of a 2  $\mu$ A driving current to the micro-LED, the error rate between the conventional 2T1C pixel circuit and the proposed pixel circuit is shown in Fig. 21. The error rate of the proposed pixel circuit is reduced significantly thanks to the IR drop

**TABLE 4.**  $V_{GATE}$  behavior at 1 frame time ( $T_{FRAME}$ ).

| Image            | 2T1C             | Proposed         | Improvement |

|------------------|------------------|------------------|-------------|

| Pattern          | Pixel Circuit    | Pixel Circuit    |             |

| <i>WB ··· WB</i> | 1.21 V (typical) | 1.63 V (typical) | 25.0 %      |

|                  | 1.27 V (worst)   | 1.71 V (worst)   | 24.3 %      |

| $BW \cdots BW$   | 1.36 V (typical) | 1.11 V (typical) | 21.9 %      |

|                  | 1.16 V (worst)   | 0.87 V (worst)   | 25.0 %      |

TABLE 5. Performance summary of the CMOS backplane.

| Parameter                  | Specification         |

|----------------------------|-----------------------|

| CMOS process technology    | 180nm                 |

| Power supply for logic/LED | 1.8 V/5 V             |

| Power dissipation          | 138.8mW* <sup>1</sup> |

| Die area                   | 13.8 mm x 9.68 mm     |

| Pixel size*2               | 10 μm x 10 μm         |

| Resolution                 | 1280RGB x 768         |

| PPI (sub-pixel base)       | 5,080                 |

<sup>&</sup>lt;sup>1</sup> Tested with the checker pattern image (BWBW...BW)

<sup>&</sup>lt;sup>2</sup> Each pixel contains 2 by 2 (RGBR) sub-pixels

FIGURE 21. Error rate with IR drop on local GND line of conventional 2T1C pixel circuit and proposed pixel circuit.

compensation of the pixel circuit. It is suppressed under 2.2 % for  $GND_{PIXEL} = 0.6 \text{ V}$  with the proposed pixel circuit.

# **B. MEAUSUREMENT RESULTS**

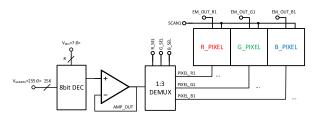

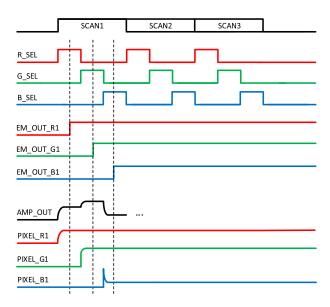

Fig. 22 shows the overall functional block diagram of the CMOS backplane with the proposed pixel circuit. It includes the peripheral circuitry that drives the pixel array, including a scan driver, source amplifiers, a separate gamma generator for RGB color, and an emission control. The RGB pixel drive scheme for the proposed sub-pixel circuit is shown in Fig. 23. It is designed to support a separated 8-bit color control for RGB. One of the 255 gray scales, which is generated by the gamma generator, is delivered through DEC to the buffer amplifier. The output of this buffer is written into each pixel by *R\_SEL*, *B\_SEL*, and *G\_SEL* through 1-to-3 DEMUX when the switch control signal (*V<sub>SCAN</sub>*) is enabled. Then it is passed to the gate of the driving transistor inside *R\_PIXEL*,

FIGURE 22. Top Block Diagram of CMOS Backplane.

FIGURE 23. Block diagram of driving RGB pixel with the proposed sub-pixel.

G\_PIXEL, or B\_PIXEL, accordingly. The timing diagram of the driving RGB pixel is shown in Fig. 24.

FIGURE 24. Timing diagram of driving RGB pixel with proposed sub-pixel.

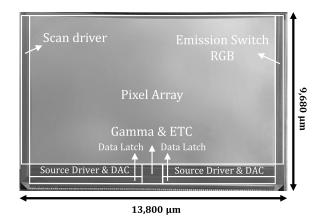

Fig. 25 shows the die photo of the finished CMOS backplane IC which is fabricated using 180 nm CMOS process technology. The average power consumption is 138.8 mW.

FIGURE 25. Die photo of the finished CMOS backplane.

FIGURE 26. Simulated and measured I<sub>PIXEL</sub> under the test pattern image. (5 line: White, Red, Green / 20line: Blue).

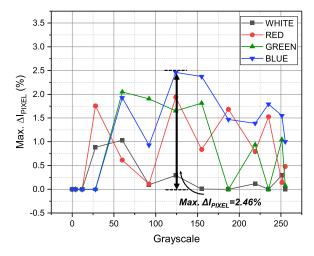

FIGURE 27. Maximum current difference (Max.  $\Delta I_{PIXEL}$ ) at different test patterns.

The sub-pixel pitch is 5  $\mu$ m and a single RGB pixel pitch is 10  $\mu$ m (2 by 2 with RGBR sub-pixel structure).

Fig. 26 shows the simulated and measured I<sub>PIXEL</sub> using the test images. In order to verify the IR drop compensation scheme of the proposed circuit, three test images were used: the top, middle, and bottom regions of the array.

(W/R/G/B)\_TAR is the simulated target  $I_{PIXEL}$ , while (W/R/G/B)\_TOP, (W/R/G/B)\_MID, and (W/R/G/B)\_BOT are the measured  $I_{PIXEL}$  in each test image. This simulation shows that the measured  $I_{PIXEL}$  fits well with the target  $I_{PIXEL}$ . Fig. 27 shows the maximum pixel current difference (Max.  $\Delta I_{PIXEL}$ ) in each test image. The  $\Delta I_{PIXEL}$  of each side is defined as (16), and Max.  $\Delta I_{PIXEL}$  is the maximum  $\Delta I_{PIXEL}$  with all the gray scales of each color.

The maximum  $\Delta I_{PIXEL}$  of the white, red, green, and blue line pattern is 1.04 %, 1.94 %, 2.05 %, and 2.46 %, respectively. This proves that the non-uniformity of the pixel current with the proposed circuit is less than 2.5 % with the whole region on display.

## **V. CONCLUSION**

In this paper, a 4T1C-based pixel circuit scheme has been introduced to address the degradation of the display image caused by the leakage current of the switch transistor, as well as the IR drop of the array. Due to the driving current, and the characteristics of its display gamma correction value, the proposed pixel circuit improves the uniformity of the display image. A detailed circuit analysis of the proposed pixel circuit, and its simulation results have been presented. The simulation and test results show that the proposed pixel circuit helps to solve the problems of the leakage current of the switch transistor and the IR drop.

#### **REFERENCES**

- MicroLED Displays 2018 Report by Yole Dévelopment, Yole Development, ment, Lyon, France, Jul. 2018.

- [2] L. Sanchez, L. Bally, B. Montmayeul, F. Fournel, J. Dafonseca, E. Augendre, L. Di Cioccio, V. Carron, T. Signamarcheix, R. Taibi, S. Mermoz, and G. Lecarpentier, "Chip to wafer direct bonding technologies for high density 3D integration," in *Proc. IEEE 62nd Electron. Compon. Technol. Conf.*, San Francisco, CA, USA, May 2012, pp. 1960–1964.

- [3] Samsung. (2018). Sony Unveils 'The Wall,' The World's First Modular MicroLED 146-Inch TV. [Online]. Available: https://new. samsung.com/global/samsung-unveils-the-wall-the-worlds-first-modular-microled-146-inch-tv

- [4] B.-C. Kwak and O.-K. Kwon, "A 2822-ppi resolution pixel circuit with high luminance uniformity for OLED microdisplays," *J. Display Technol.*, vol. 12, no. 10, pp. 1083–1088, Oct. 2016.

- [5] Z. Liu, K. Zhang, Y. Liu, S. Yan, H. S. Kwok, J. Deen, and X. Sun, "Fully multi-functional GaN-based micro-LEDs for 2500 PPI micro-displays, temperature sensing, light energy harvesting, and light detection," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2018, pp. 38.1.1–38.1.4.

- [6] S.-W. Eo, J. G. Lee, M.-S. Kim, and Y.-C. Ko, "High performance and low power timing controller design for LCoS microdisplay system," in *Proc. Int. Soc Design Conf. (ISOCC)*, Seoul, South Korea, Nov. 2017, pp. 71–72.

- [7] U. Vogel, P. Wartenberg, B. Richter, S. Brenner, K. Fehse, and M. Schober, "OLED-on-Silicon microdisplays: Technology, devices, applications," in Proc. 48th Eur. Solid-State Device Res. Conf. (ESSDERC), Dresden, Germany, Sep. 2018, pp. 90–93.

- [8] K. Strickland, "52-5: Late-news paper: The future of MicroLED displays using next-generation technologies," in SID Symp. Dig. Tech. Papers, May 2018, vol. 49, no. 1, pp. 696–697, doi: 10.1002/sdtp.12354.

- [9] A. Paranjpe, J. Montgomery, S. M. Lee, and C. Morath, "45-2: Invited paper: Micro-LED displays: Key manufacturing challenges and solutions," in *SID Int. Symp Dig. Tech Papers.*, vol. 49, May 2018, pp. 597–600, doi: 10.1002/sdtp.12414.

- [10] S. Ono, K. Miwa, Y. Maekawa, and T. Tsujimura, "V<sub>T</sub> compensation circuit for AM OLED displays composed of two TFTs and one capacitor," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 462–467, Mar. 2007.

- [11] J. G. Um, D. Y. Jeong, Y. Jung, J. K. Moon, Y. H. Jung, S. Kim, S. H. Kim, J. S. Lee, and J. Jang, "Active-matrix GaN μ-LED display using oxide thin-film transistor backplane and flip chip LED bonding," *Adv. Electron. Mater.*, vol. 5, no. 3, Mar. 2019, Art. no. 1800617, doi: 10. 1002/aelm.201800617.

- [12] X. Guan, S. Jian, P. Hongda, Z. Zhiguo, and G. Haibin, "An image enhancement method based on gamma correction," in *Proc. 2nd Int. Symp. Comput. Intell. Design*, Dec. 2009, pp. 60–63.

- [13] C. Hu, "MOSFETs in ICs—Scaling, leakage, and other topics," in *Modern Semiconductor Devices for Integrated Circuits*, 1st ed. New York, NY, USA: Pearson, 2009, pp. 263–269.

- [14] B. G. Park, S. W. Hwang, Y. J. Park, Nanoelectronic Devices, 1st ed. Boca Raton, FL, USA: CRC Press, 2012, pp. 199–202.

- [15] K. Zhang, D. Peng, W. C. Chong, K. M. Lau, and Z. Liu, "Investigation of photon-generated leakage current for high-performance active matrix micro-LED displays," *IEEE Trans. Electron Devices*, vol. 63, no. 12, pp. 4832–4838, Dec. 2016, doi: 10.1109/TED.2016.2619119.

- [16] C.-L. Fan, Y.-C. Chen, C.-C. Yang, Y.-K. Tsai, and B.-R. Huang, "Novel LTPS-TFT pixel circuit with OLED luminance compensation for 3D AMOLED displays," *J. Display Technol.*, vol. 12, no. 5, pp. 425–428, May 2016.

- [17] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, Feb. 2003.

- [18] M. J. Deen and Z. X. Yan, "DIBL in short-channel NMOS devices at 77 k," IEEE Trans. Electron Devices, vol. 39, no. 4, pp. 908–915, Apr. 1992.

- [19] J.-P. Lee, H.-S. Jeon, D.-S. Moon, and B. S. Bae, "Threshold voltage and IR drop compensation of an AMOLED pixel circuit without a V<sub>DD</sub> line," IEEE Electron Device Lett., vol. 35, no. 1, pp. 72–74, Jan. 2014.

- [20] A. R. Chen, A. I. Akinwande, and H.-S. Lee, "A CMOS-based microdisplay with calibrated backplane," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, vol. 1, 2005, pp. 552–617.

JEWOO SEONG was born in Geoje, South Korea, in 1994. He received the B.S. degree in electrical engineering from the Ulsan National Institute of Science and Technology (UNIST), South Korea, in 2016, where he is currently pursuing the combined M.S./Ph.D. degree. His research interests include analog/mixed-signal integrated circuits for automotive electronics, and display driver IC, especially in-vehicle networks and source driver IC.

JINWOONG JANG received the B.S. degree in electronic engineering from the Kumoh National Institute of Technology, South Korea, in 2014. In 2015, he joined CrucialTec, South Korea, where he was an Analog Engineer involving in design fingerprint sensors and PMOLED drivers, until 2017. He is currently a Researcher with Sapien Semiconductors, South Korea. He is interested in small size MicroLED driver circuits and microdisplay backplane ICs.

JAEHOON LEE received the B.S. degree in electronic engineering from Pusan National University, South Korea, in 1990. He joined Samsung Electronics, South Korea, where he was worked for 25 years. He was in charge of analog IC design and application. He is currently the R&D Head of Sapien Semiconductors, South Korea. He is interested in small size MicroLED driver circuits and microdisplay backplane ICs.

**MYUNGHEE LEE** (Member, IEEE) received the B.S. degree in electronic engineering from Hanyang University, Seoul, South Korea, in 1984, the M.S. degree in electrical engineering from Arizona State University, Tempe, AZ, USA, in 1990, and the Ph.D. degree in electrical engineering from the Georgia Institute of Technology, Atlanta, GA, USA. He started his industry career as a Hardware Engineer at Doosan Computer Corporation, from 1984 to 1988. From 1990 to 1991, he worked as

an Engineer at IBM T. J. Watson Lab, Hawthorne, NY, USA, before he resumes his Ph.D. course. In 1996, he joined Hewlett Packard (later Agilent Technology after the break-up of the company), San Jose, CA, USA, as a Member of Technical Staff, developing IrDA transceiver ICs and Giga-bit fiber-optic transceiver ICs, including 4-ch/12-ch parallel optical transceivers. Later, he was promoted to the position of Integrating Manager, managing a world-wide R&D organization responsible for various high-speed IC product development projects. In 2005, he joined Samsung System-LSI Division as a VP in Giheung, South Korea, managing the Display Driver IC (DDI) Development Team. He was responsible for developing various product families, such as mobile-DDIs, panel-DDIs, timing controllers, and touch sensor controller. From 2012 to 2013, he worked for Hyundai-Autron, leading the Automotive Semiconductor Development Centre managing automotive Electronic Control Units (ECUs) and automotive IC development activities. Since 2013, he has been serving as an Industry-University Collaboration Professor, Ulsan National Institute of Science and Technology (UNIST), Ulsan, South Korea. His research interests include automotive ECU architecture, innovative automotive IC architecture and implementations, various high-speed interfaces, and various other mixed-signal IC designs.

...